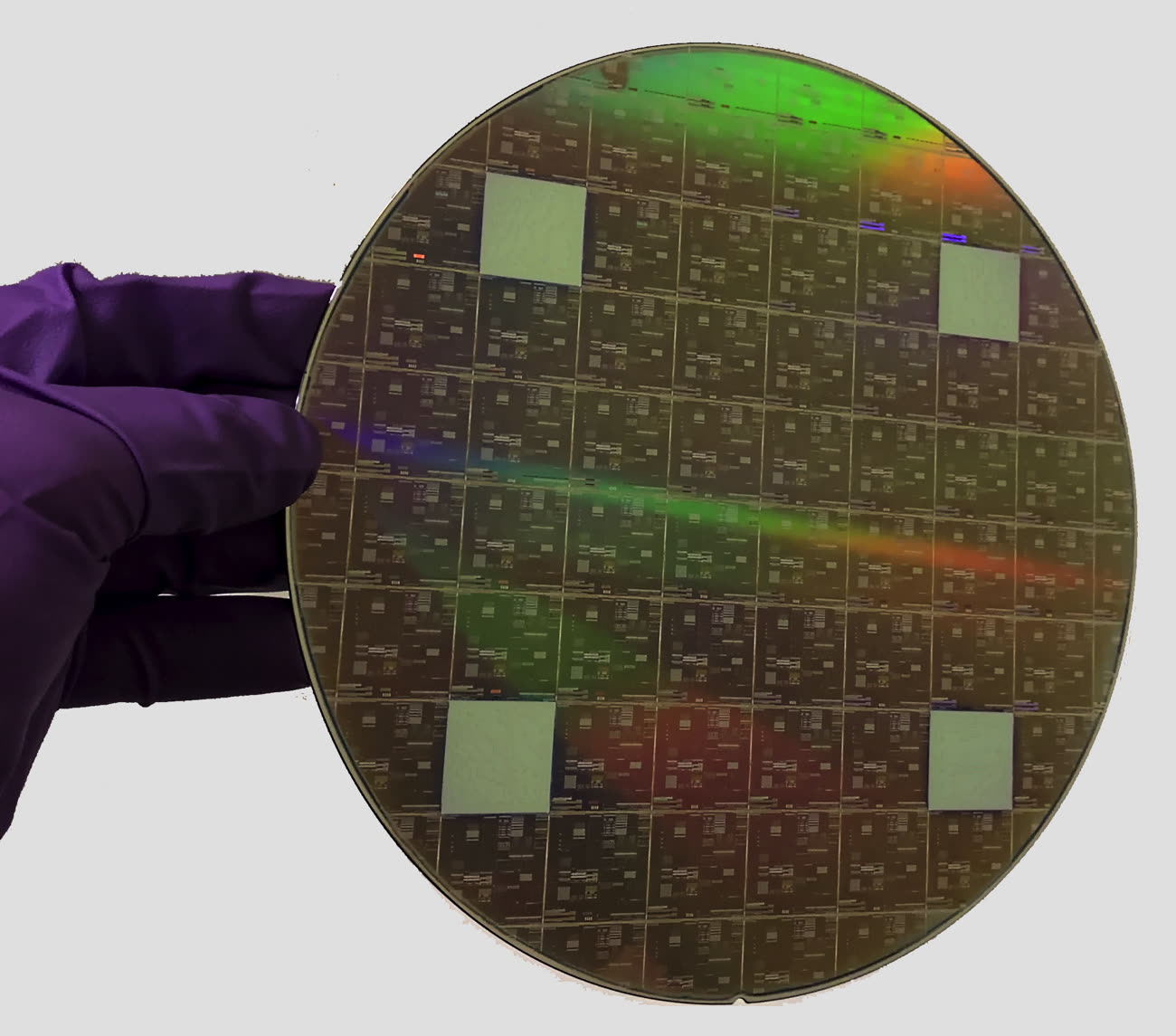

Alors que TSMC fête le lancement de la production de masse de puces gravées à 3 nm, la concurrence est face à un dilemme : faut-il suivre le mouvement ? Selon un rapport de Digitimes, Qualcomm et MediaTek ne sont pas encore sûrs de lancer la production en 2023. Apple pourrait donc garder l'exclusivité sur cette technologie un certain temps.

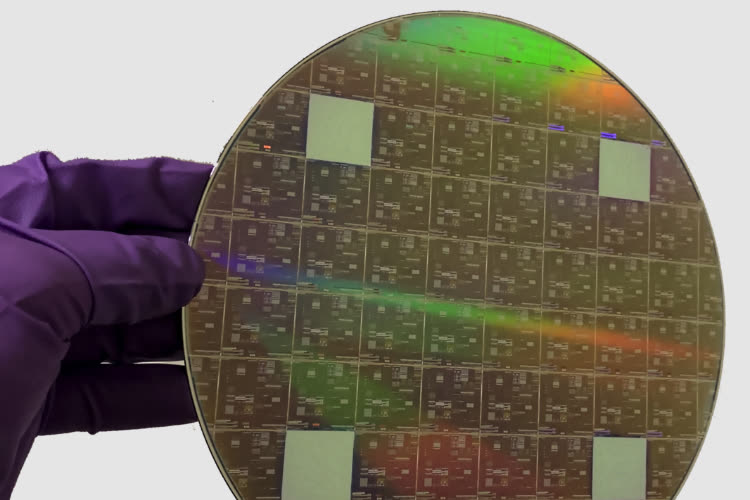

La raison de cette hésitation se cacherait derrière des « des perspectives de vente peu claires pour les appareils Android ». La source interrogée par le site ajoute que le coût de fabrication de la technologie 3 nm dépasse les 20 000 dollars par wafer, ce qui serait dissuasif alors que la demande se tarit. En comparaison, Digitimes affirmait le mois dernier que le wafer 5 nm coûtait 16 000 $.

Qualcomm fournit les puces de nombreux téléphones Android, notamment celles de Samsung (le plus gros concurrent direct d'Apple). Si le fabricant coréen décide d'emboiter le pas à Cupertino, Qualcomm risque de ne pas avoir d'autre choix que de passer à la gravure en 3 nm. De son côté, MediaTek fournit les puces de certains smartphones Oppo, Asus et Xiaomi.

Selon les rumeurs, les premières puces d'Apple gravées à 3 nm seraient les M2 Pro et M2 Max que l'on retrouverait dans de futures révisions des MacBook Pro 14" et 16". Le prochain SoC de l'iPhone 15 Pro (et Ultra ?) devrait également profiter de cette technologie.

Source :