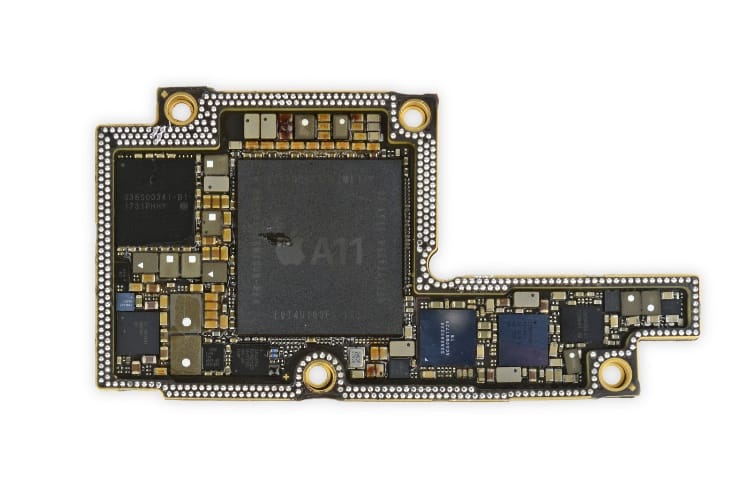

Ming-Chi Kuo : le 2 nm arriverait dès 2026 chez Apple

Si la puce A17 Pro est la première puce Apple gravée à 3nm, Cupertino est sans doute déjà en train de préparer les futures générations de ses SoC Apple Silicon. L'analyste Ming-Chi Kuo estime que les premières puces à 2nm pourraient arriver pas plus tard qu'en 2026. Apple serait un des premiers clients pour ses processeurs d'iPhone, au côté de NVIDIA, qui compte bien utiliser la technologie pour ses puces spécialisées sur l'intelligence artificielle.

Un tel calendrier serait semblable à celui de l'utilisation de la gravure à 5nm. Apple a utilisé cette technologie pendant 3 ans pour ses puces A14, A15 et A16. On peut imaginer que les puces A17 Pro, « A18 » et « A19 » seront elles aussi à 3nm. Le passage au 2nm se ferait avec l'iPhone 18 et sa puce « A20 ».

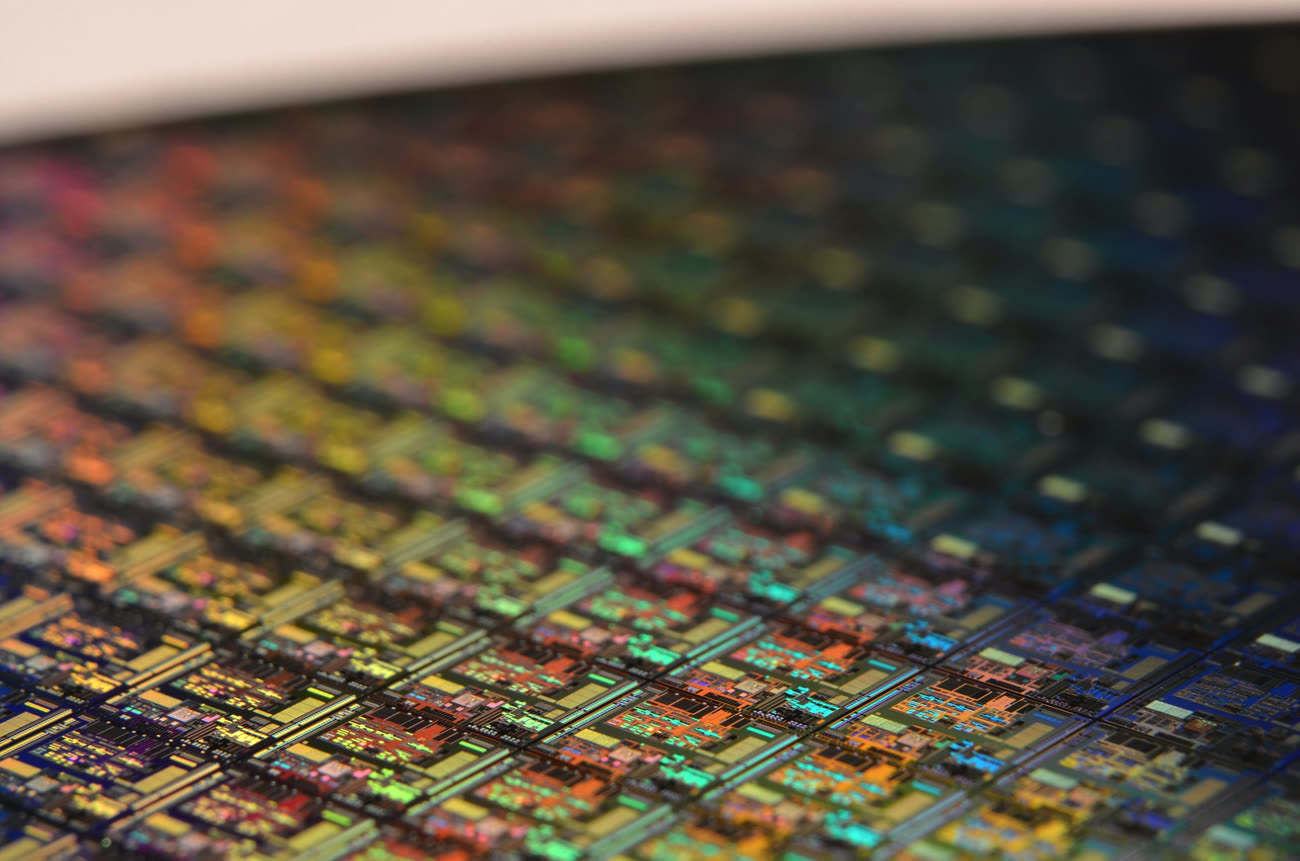

Cette prévision va dans le sens de ce qu'a annoncé l'industrie. TSMC voit arriver une production en masse de puces gravées à 2nm pour la fin de l'année 2025, ce qui veut dire que le premier iPhone en intégrant une pourrait être l'iPhone 18 de 2026. Le procédé semble prometteur : il devrait apporter un nouveau mode d'alimentation de la puce améliorant l'efficacité énergétique.

Pour l'ergonomie le 15 n'est pas trop mal, exit bords carrés, réduction drastique du poids , taille correcte...pour ce qui est de la batterie par contre ..c'est bien là que se situe mon inquiétude, et les tests que j'ai lus ne sont pas vraiment élogieux...déjà que le 14 pro était loin d'être fabuleux, c'est plutôt inquiétant

Apple aurait pu augmenter la batterie j'en suis presque sur...quand on voit le s23 avec 3900mah, comparé aux 32xx anémiques de l'iPhone . Mais bon . Après , il faut se rappeler que les iPhones avaient une batterie catastrophique avant la série 11

@ratz

1800 mAh pour l’iPhone 6

La principale nouveauté du 2nm n’est pas l’alignement.

Il y a 2 grosses innovations:

- l’abandon du Thin FET ntroduit chez TSMC en 2011 pour le GaAFET ou Gate all around. En gros, la gate du transistor est controlée sur toute sa surface permettant d’augmenter la densité en rapprochant la distance physique entre 2 transistors

- l’introduction d’un nouveau scanner de la part d’ASML dit EUV High NA qui permet d’augmenter la résolution de gravure et au moins pour le 2nm d’aller plus vite qu’avec les anciens scanner

Cependant il y a un effet kiss cool: la taille ma imale de la die passe de 858 à 429mm2. Le hic c’est qu’avec la position dominante de Nvidia, ils ont souvent trusté avec des tailles autour des 600mm2. Avec cette taille ils n’arrivent qu’à pondre très peu puces valides par wafer. Et du coup cela des coûts exorbitants sachàt qu’ils margent à 70%. Mais sans concurrence, pourquoi faire plus compliquer?

Avec le 2nm ils n’auront pas de choix que de passer aux chiplets comme AMD qui l’a fait pour avoir des prix plus aggressifs…

Pages