Un des développeurs de Debian a mis en lumière un bug touchant la fonction Hyper-Threading des processeurs Intel de génération Skylake et Kaby Lake, ainsi que les Xeon v5 et v6.

Ce bug, qui concerne tous les systèmes d’exploitation, peut causer des erreurs, dont des pertes de données. En janvier, un développeur d’OCaml, une implémentation du langage de programmation Caml, disait avoir constaté des erreurs sur deux MacBook Pro 15" fin 2016 (Core i7–6820HQ).

La fonction Hyper-Threading, qui double virtuellement le nombre de cœurs pour augmenter les performances, est disponible sur les Core i7 ainsi que certains Core i5. Les Mac équipés de processeurs Skylake ou Kaby Lake avec Hyper-Threading sont les iMac Retina 5K Core i7 fin 2015 et 2017, ainsi que les MacBook Pro 2016 et 2017.

Intel a identifié le problème, mais il faut maintenant que les constructeurs publient une mise à jour du BIOS ou de l’EFI contenant les correctifs. Apple ne semble pas l’avoir fait pour le moment.

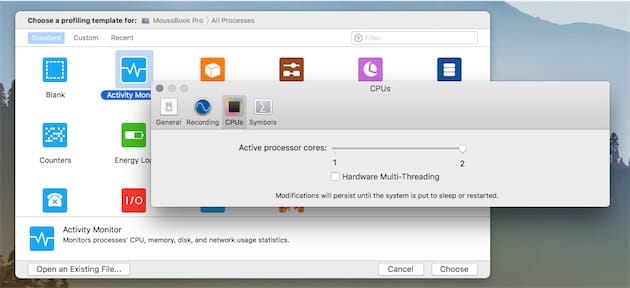

Si vous remarquez des bugs sur votre Mac qui fait partie de ceux concernés, vous pouvez désactiver l’Hyper-Threading en ouvrant l’application Instruments fournie avec Xcode (utilisez Spotlight pour l’ouvrir), puis en décochant « Hardware Multi-Threading » dans la section CPUs des préférences. Attention, l’Hyper-Threading se réactive après la mise en veille ou le redémarrage.