Une rumeur indique qu'Apple pourrait passer sur la technologie System on Integrated Chip de TSMC pour ses futures puces M5. Et nous allons le voir, ce n'est pas un changement anodin, tant les quelques solutions qui en profitent actuellement permettent des gains intéressants.

Il ne s'agit ici que d'une rumeur issue d'Economic Daily, mais la technologie est intéressante pour Apple et dans la droite ligne des différentes optimisations apportées aux puces M au fil du temps. La technologie SoIC de TSMC permet de façon très schématique de créer des puces en 3D, empilées. Le but principal, dans la majorité des cas, est d'ajouter de la mémoire directement sur le système sur puce, en la plaçant au plus près des composants.

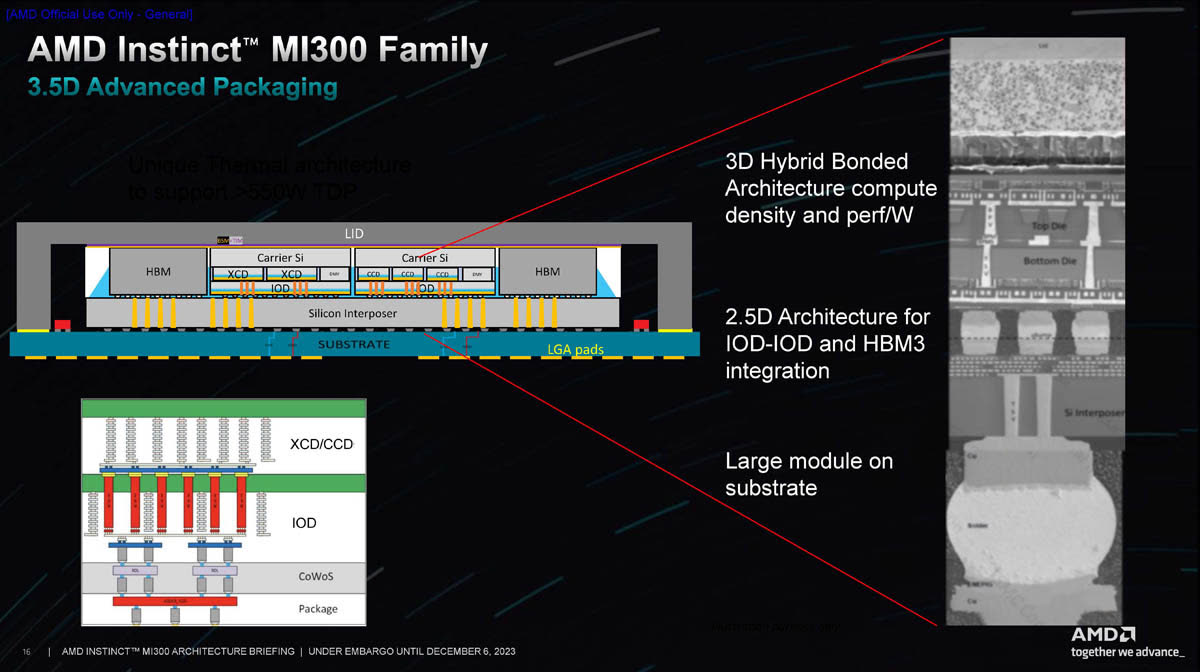

AMD utilise la technologie depuis quelques années maintenant dans ses Ryzen 3D et dans certaines variantes des puces EPYC (ses processeurs pour les serveurs). Dans ce cas de figure, AMD ajoute de la mémoire cache de niveau 3, avec une capacité élevée (64 Mo). L'augmentation de la mémoire cache améliore très largement les performances dans les jeux (pour les Ryzen) ou dans beaucoup de tâches liées aux serveurs pour les EPYC. Dans d'autres puces, comme les récents MI300, c'est de la mémoire vive de type HBM qui est placée au-dessus des autres composants, pour offrir une bande passante très élevée à des puces pensées pour l'accélération des calculs liés aux IA.

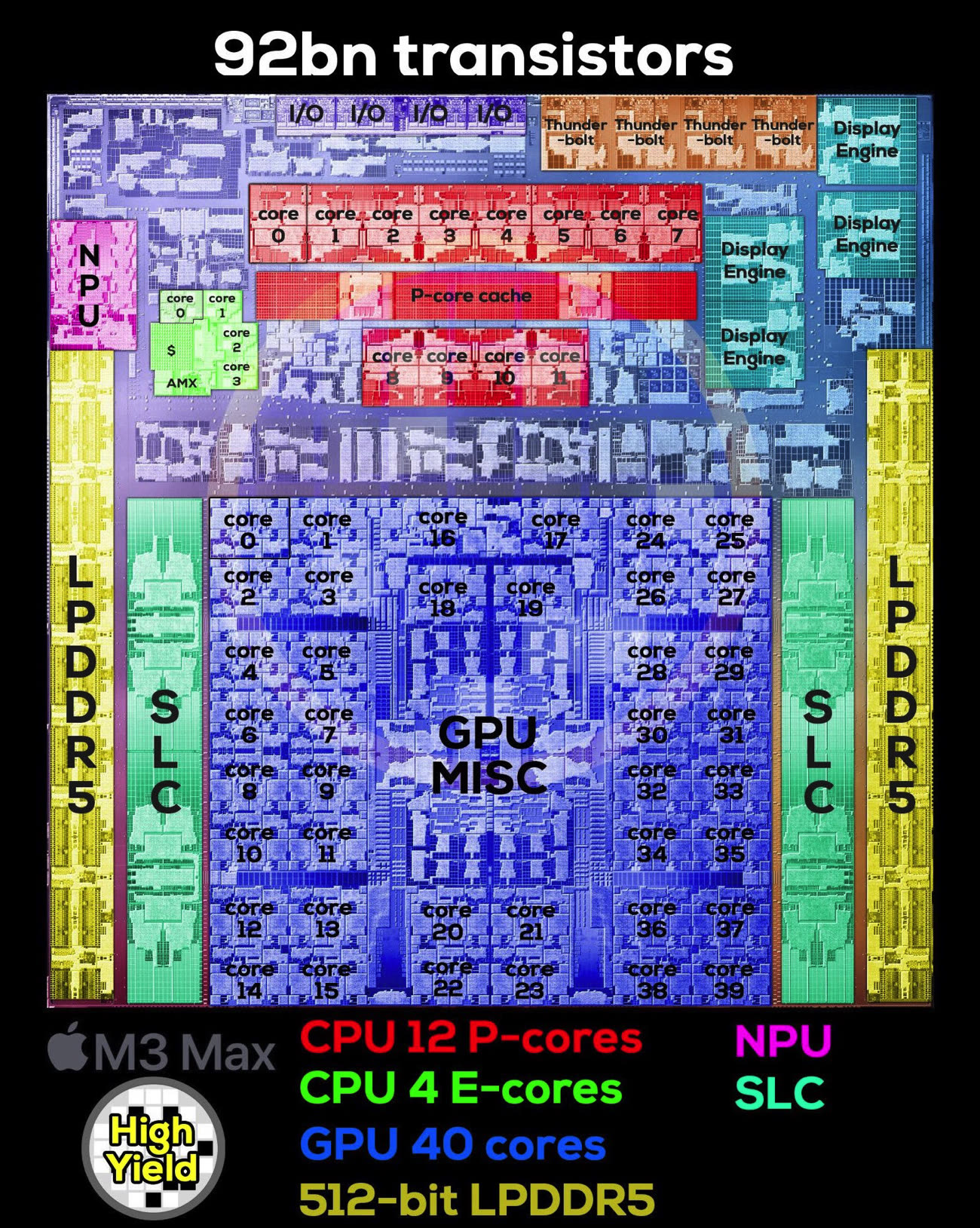

Les rumeurs évoquées par nos confrères de MacRumors évoquent autant les futurs Mac que les puces dédiées aux serveurs — Apple utiliserait pour le moment des puces M2 Ultra — pour cette solution, et différentes voies existent. La première serait d'augmenter très largement la capacité du cache dit SLC (System Level Cache) des puces. Ce dernier niveau de mémoire cache se place entre la RAM et les autres composants du système sur puce (CPU et GPU), et augmenter sa capacité améliorerait très nettement les performances. Sans la solution d'empilement de TSMC, les possibilités sur ce point restent assez faibles : il est souvent plus intéressant de réserver les transistors à des fonctions supplémentaires plutôt qu'à une augmentation massive d'une mémoire cache.

L'autre solution serait d'intégrer la mémoire directement sur le système sur puce, pour (encore) augmenter la largeur du bus et donc les performances. Actuellement, Apple intègre un bus qui peut atteindre 512 bits (sur les puces M3 Max, le double sur les variantes Ultra) mais l'intégration n'est pas simple. En effet, en plaçant les puces de mémoire à côté des composants, Apple doit structurer ses puces pour placer les différentes interfaces… sur les côtés, justement. En passant sur des puces empilées, il deviendrait possible d'avoir un peu plus de flexibilité sur ce point, et même à intégrer un bus plus large.

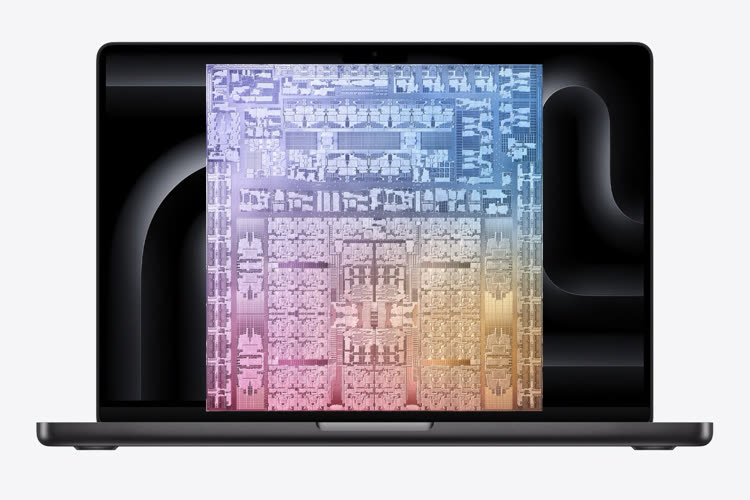

Une analyse commentée des puces Apple M3

Dans tous les cas, même si la puce M4 n'est pour le moment disponible que dans les iPad Pro, les rumeurs sur les futures puces M5 sont déjà bien là.